�����r�g4��21�գ����ò��Ϲ�˾�e�k��ȫ���s֮�ôࡣ�ڴ����g���҂����cӑՓ��оƬ��������δ�������߾��w���ܶȵăɗl;����һ�����m���yĦ�����ɵĶ��S�s����ʹ��EUV��̺Ͳ��Ϲ��̄����˸�С�����ԡ���һ�N���OӋ���g�ąfͬ������DTCO���Լ����S���ܣ����������߉��Ԫ�IJ��֣��Ա��ڲ���׃��̖ž����r�������ܶȡ��������xȡӢ�IJ���ԭ�ģ�����n�̵ļ��g���衣

оƬ��ُ�W��ע�����χ������ڙ�IC�����̬F؛�YԴ��оƬ��挍�r��ԃ���ИI�r���������ُ����ICоƬ�����Ȍ��IоƬ��ُƽ�_��

����S�s�İlչ

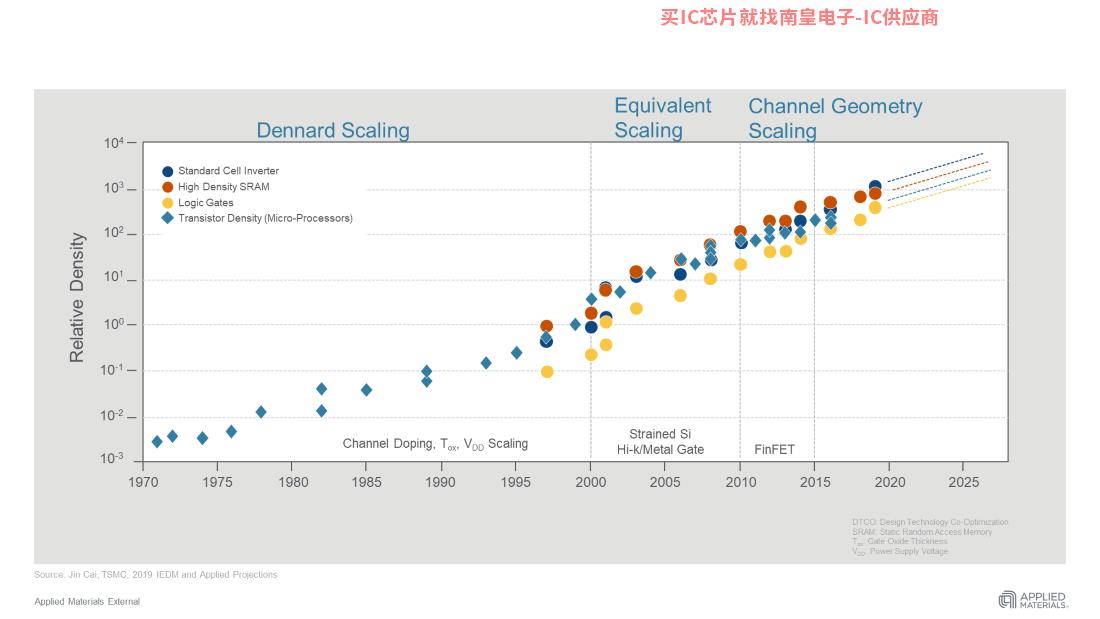

������֪�����y��Ħ�����ɶ��S�s���x��оƬ�ИI�낀�����o�ԁ��ļ��g�lչ·���D���ڵ��{��2000�����ҵ��s�r�����҂�ÿ���ꌢ���w�ܳߴ�p��50%�����ڿ��ƾ��w���_�P��B�ĖŘO�����L�ȶ��x�鹝�c��90�{�ס�65�{�ȡ��҂��������ŘO�ɱ����sС��оƬ�������������ܡ����ʺ���e�ɱ�(��PPAC)ͬ�����M������^ȥ���@Щ�M����������ף�

��2000�굽2010�꣬�ŘO�L�Ⱥ������ŘO�s�_���O�ޣ��҂����ԈD�λ��^С�����������]�����톖�}����ŘOй©�ͽ��|��裬�@������������e�ɱ����������ܺ���Ч�档��ˣ��҂��^�ɵ���Ч�s���c���Q�����c���H�ߴ���^���D�����Ñ�׃���Kֵ���ٖŘO�Ȳ��Ϲ��̹�ˇ���@�ӣ���ʹ��e�ͳɱ���AC���҂���Ȼ���Ա������ܺ��ʵĸ��M�ž���PP����Ч�档2010���Ժ����SFinFET�Y�����Q����ʹ��PP��AC��һ�Әǡ�

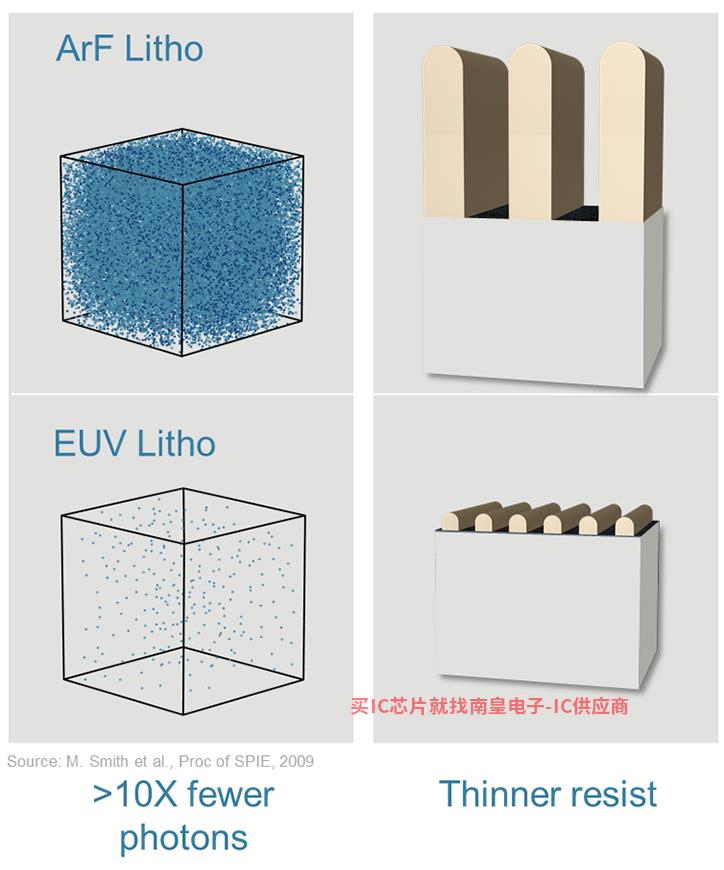

����̼��gͣ����193�{���]�r�����Ϲ���Ҳ�l�]�����á������γ̈D�λ������ڼs80�{�ĸ�ž��x���p�D�λ����ĈD�λ��քeʹ�s�����Mһ���_��40�{��20�{�ĸ�ž��x��

�˽�EUV(�O���⾀)-ʹ�D�θ����Σ���ʹ���������s

���lչ��5�{���c�r��EUVԓ���g���\���������F��25�{����g��ĈD�λ������ǣ���EUV�����ã���Ҫ�µIJ��Ϲ��̼��g�����磬��EUV�ڷֱ��ʘO��ˮƽ�ϣ����y���������䷽�����y�þ��w�ܽ��|ͨ�������١����ڽ��ٲ�����e̫С�����|����ָ�����ӡ�ͬ�r�����ɲ��Ͻ�Q������Integrated Materials Solutions���x���Խ��|���e������ȡ������ӣ�ͬ�r�a���^���ĵ������|�c��

�µ��s������������

1.�Mһ��EUV�s�ķ���

�Л]���µķ��������Mһ���sС�ߴ磿���ǿ϶��ģ������ɗl·:

�� ���m�ăȲ��s�������m���y�Ķ��SĦ�����ɡ�EUV��̺Ͳ��Ϲ��̄����˸�С�����ԡ�Ħ������ʹ3�{���c��߉�ܶ�������һ�����ҡ�

�� �fͬ�������ü��g��DTCO�������߉��Ԫ���֣����3�{���c��һ���߉�ܶȡ�

2.EUV���Ϲ������R�µ�����

ʹ��EUV���g���ɹ��ӷdz����y�Ͱ��F����ˣ��҂���ԓEUV���ʹ�õĹ��Ӕ���ֻ����������g��ʮ��֮һ�����⣬�҂�ʹ����EUV�g�̵ĈD��(�罻�澀�l���g��)���öࡣEUV����z�ĺ��Ҳ����ͣ������҂������ø��ٵĹ����_�l����ģ�D�Σ��@Ҳ�����ڷ�ֹ���D��̮��ճ����

��4��21�յĴ��n�ϣ��҂�ӑՓ��ʹ��EUVȻ���^�mоƬ���s��ǰ�����҂�����ͬ�r��Q���Ϲ��̺͜y�������������P�I���}�����£�

�� ���}1���m��EUV����z���S�C�`��

�� ���}�����p��EUV�D�λ��ɱ�

�� ���}3�����MEUV�D��Ϳ�ӵľ���

�� ���}4���_������z�D���ڿ��g���Aǰ�ı����

�� ���}��:��Q߅�������e�`

�� ���}��:���ô����˹����ܼӿ��Mչ

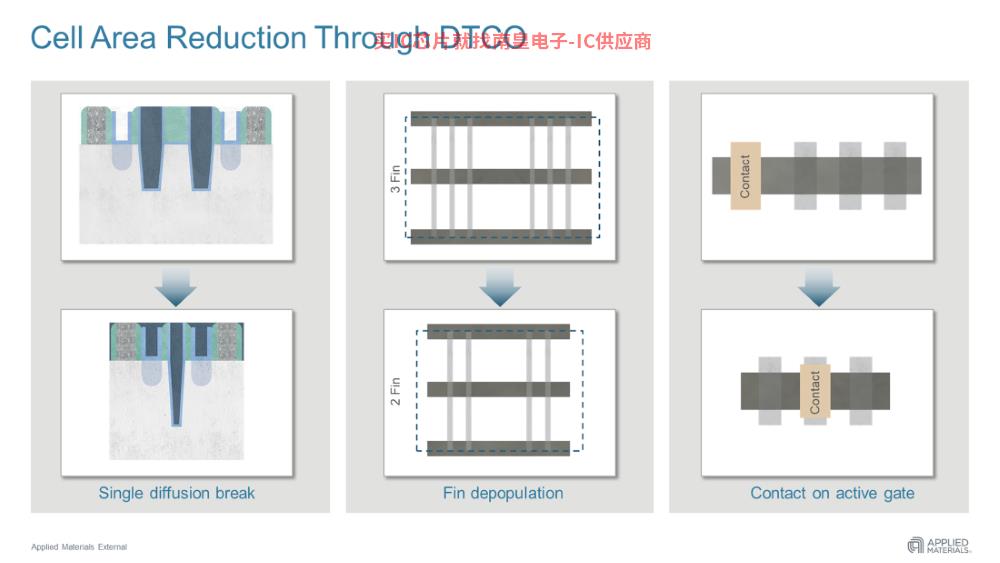

�fͬ�������ü��g��DTCO���ͭh�@�ŘO��GAA�����w��

������������3�{���c��50%��߉�ܶȁ��ԃȲ��s�������y�Ķ��S�s������50%����DTCOҲ�����f���OӋ���g�fͬ�����������s���ИI������50���꣬������F��DTCO�����ڏ��a���yĦ�������s�ķž���DTCO���µķ����ǿsС߉��Ԫ�������ܶȣ������e�ɱ���

1.�J�RDTCO

DTCO ����ָ�ڲ���׃��̖ž����r�£�����ظ�׃߉��ԪԪ���IJ��֣����F���w�ܵ��Mһ���s���F���ЎNDTCOоƬ�OӋ��ʹ�õļ��ɡ����磬�ڸ��x��߉��Ԫ�r���OӋ���ÆΔUɢ�����p�Uɢ���Ķ��_�����@���sЧ�����OӋ��߀��ÿ�����w�ܵ���Ƭ���������p�ٵ��ɂ����Q��p����fin depopulation��̎����ͬ�ӣ��OӋ��Ҳ��Ŭ�����F�ŘO���|�c��contact over gate����Ҳ�����f�����w�ܵ�늽��|�Ă����Ƶ�픲���

��4��MMD������21�յĴ��n�ϣ��҂���B��һ��µĄ��³ɹ��������ژO���w�ܡ���ʹ������DTCOͬ�r���оƬ�����ܺ��ʡ�

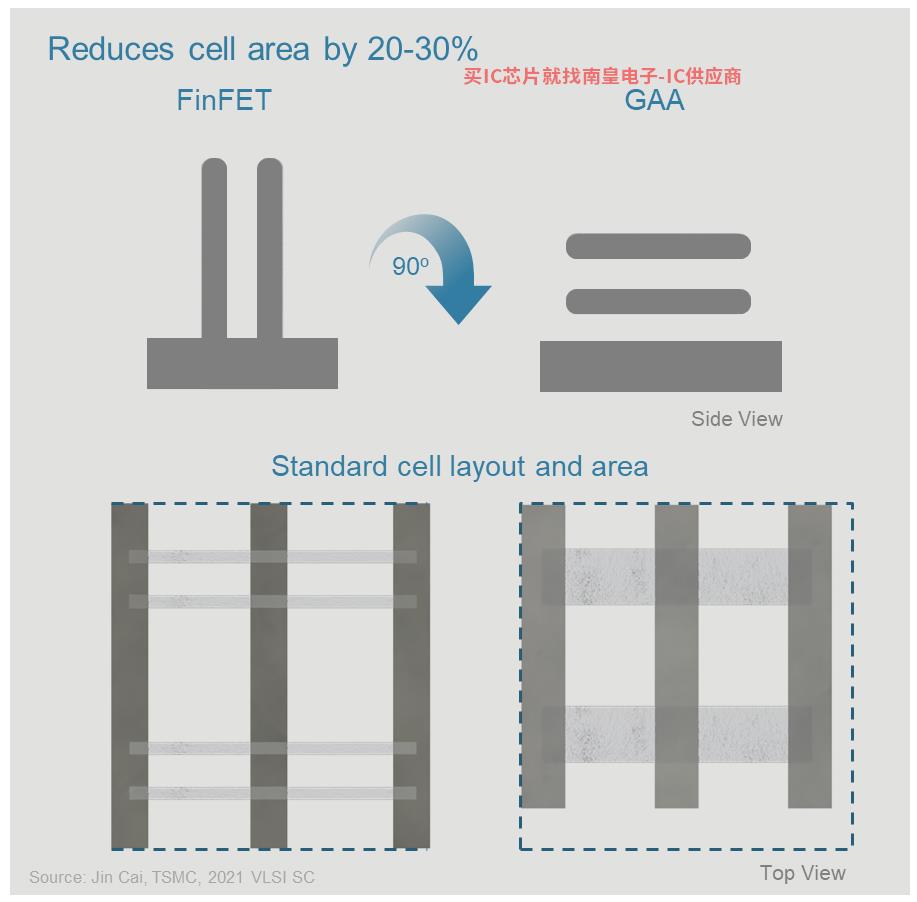

2.�˽�h�@�ŘO���w��

2010�꣬FinFETоƬ�OӋ��־����ƽ����S���w�ܵ����S���w�ܵ�оƬ�OӋ����GAA�����w�܌��ɞ��^FinFET֮��оƬ�ИI�����OӋ�D��֮һ��

��GAA�����ɡ�DTCOһ�N��ʽ���ܿ��������ϳ��������_������DTCO�Ķ��x��GAAͨ�^�������ž��w��Ԫ������ͬһ��̖ž����F����FinFET߉�ܶȡ����\���ǣ����GAA���Ϲ��̄��������߹��ʺ����ܡ������҂�����һ��BGAA���s��e��Ч����̽ӑ�������L���x�����g�̵ĸ�����;������ጼ��ɲ��Ͻ�Q������Integrated Materials Solutions���������GAA���w��ռ�ø�С�Ŀ��g���l�]��������á�

�������v��GAA�����ǰ�FinFET���w�����D90�ȡ��ŘO�h�@�����еĜϵ�������ֻ����������Ĝϵ�FinFET����һ����DTCO߉��Ԫ��X��Y������sС���ڱ������ܲ�׃����r�£��OӋ�����Դ����e�ɱ���Ȼ�����������ܸ��п��ܲ�ȡ��һ�N�������ӌ��{��Ƭ��������������Ķ����25%�����ܺ�25%���ܶȡ�

�������L���x���Ը��gGAA���ʺ����������P��Ҫ��Ӱ�

������ĽǶȁ�����GAA���˺ܶ�����FinFET���칤ˇ�����P�I�^�e������δ_���Ϳ��ƜϵČ��Ⱥ;����ԡ�FinFET��ͨ�������ɹ�̺Ϳ��g�Q�������ҳ�����׃�ԣ��@�����;��w�ܵ����ܡ�GAA��ͨ�^���ʴ_���������L���x���Ե��g�́����x�ό����Ķ����F���ߵĜϾ����Ժ;��w�����ܡ�

GAA���ÃɷN�������L������ȫ�������L��blanket epitaxy�����ڳ��e�����Ӻ��N�ӣ��γɼ{��Ƭ�Y�����S�������x�����������L��selective epitaxy�����������OӋ�����ڼ{��Ƭ�νY�����ԃ������w�ܵ����ܡ�����x�����g������ȥ�����N�ӡ����@Щ���N���Ǡ����ӣ��H�����o�����w�����ͨ�����γɡ�

���ɲ��Ͻ�Q�������p�������ŘO��Kֵ���ٖŘO���·���

ͨ����Ҫ�Mһ���OӋ������߾��w�ܵ����ܡ��҂���Ҫ���܇�������ͨ���г��eһ���ŘO�����ӡ������ŘOԽ���������Խ�ߣ������_�P���ܣ���й©���Խ�ͣ��Ķ��p�ٹ������M�ͼӟᡣ���ϣ������ŘO�s�ѽ�ͣ�����꣬�@һͻ�Ɵo����оƬ�����̵ĺ���Ϣ��

�����������ŘO����Kֵ���ٖŘO�ѯB��������Kֵ���ٖŘO�ѯBؓ؟���ƾ��w���_�P��B���OӋ�@�N�ŘO�����y�����GAA��ͨ�g��ͨ��ֻ��10�{�ף��hС��FinFET���g�ࡣ��Ҫ���T�OӋ���ٖŘO�ѯB�Č��ȣ��ԃ���оƬ�Ĺ��ʺ����ܣ�ᘌ��ض��ĽK���Ј�����늳ع���Ƅ��O�䵽�����ܷ��������ИI��Ҫһ����Q�����������ں�С�Ŀ��g�Ȍ��F�ֵ�{�C��

���ò��Ϲ�˾�ѽ��ʂ�ø��w��V�����I��GAA����aƷ�������µ����a���E�������������L��ԭ�ӌӳ��e���x�����g�̣��Լ��ɂ��µ���������GAA�����ŘO�ͽ��ٖŘO�ļ��ɲ��Ͻ�Q������Integrated Materials Solutions����

������:���w�ܺ�оƬ߀�ܿsС��ʲô�̶ȣ�

���4��21�յ�ȫ���s֮�ô��n��Ԕ����B�˃ɷN�s����:ʹ��EUV���M���yĦ�����ɵĶ��S�s��ʹ��DTCO���ɣ��硰GAA���w��)������EUV���s�����R�������LjD�λ��������S�����w�ܽ��|�c�Ͳ����IJ���sС������ָ�����L���������r�g5��26�յĴ��n�ϣ��҂����^�mӑՓ�@Щ�����˽ⱳ����늾W�j�ͮ������ɡ�

- ��һ������Ƭ���f�����h�R������ �ƌW�҂����˺��L�r�g��������Ƭ���_��ʲô

- ���錦���N��Ӱ푼�2021��չ��

- ��˼�Ƽ�����OPPO�����аlоƬȫ�^���OӋ���ṩܛ����ȫ��Q����

- ��˹���Ԅ��{�ˎ��

- 2022�꣬����Ԫ�ǘs�@������֪�R�a��ԇ�c��λ�J�� չʾ���Č������ֳɹ�

- EDA���ҹ����о���������-�A�����EDA���ҹ����о�������ʽ�{����ҹ����о�����

- VIAVI����Rakuten Symphony�������M5G Open vRAN������~�����

- ����500���J�ɰ�ɭ����׃��֮·

- ȥ����ӯ�� ����16.8��

- ��ꐄń�Ħ���_�� Razr 2022:���C�r�g�@ϲ��չ���OӋ�ع�

- ʿ�m���SiC��һ�l�Դ�������a������ͨ��SiC�O��оƬͶƬ�ɹ�

- ����:�����F����̓�M�F�������F��