��(sh��)ģ��� IC ͨ����ģ�M�·�ǿ���ģ�M�·���F(xi��n)�ض��㷨�ĺ��ġ� IC �O(sh��)Ӌ���֣�EDA ܛ����Ҫ��ģ�M IC �͔�(sh��)�� IC ����O(sh��)Ӌܛ����

оƬ��ُ�W(w��ng)��ע�����χ���(n��i)���ڙ�(qu��n)IC�����̬F(xi��n)؛�YԴ��оƬ��挍�r��ԃ���ИI(y��)�r���������ُ����ICоƬ������(n��i)���I(y��)оƬ��ُƽ�_��

1.EDA�댧�w�ʹ��ϵ�����

1.1. EDA ������ IC ���I(y��)ܛ�����O(sh��)Ӌ�����a(ch��n)

EDA ���I(y��)ܛ�������o����Ҏ(gu��)ģ�����·���O(sh��)Ӌ�����a(ch��n)��EDA ȫ�Q������O(sh��)Ӌ�Ԅӻ���Electronic Design Automation������ָ�����o���O(sh��)Ӌ�����졢���b�͜yԇ�����ͼ����·оƬ�������^�̵�Ӌ��Cܛ�����S��оƬ�O(sh��)Ӌ���s�ԵIJ�����ߣ��������M��ˇ��(ji��)�c�ļ����·Ҏ(gu��)ģ�����_����(sh��)ʮ�|���댧�w�O(sh��)�䣬����Ҫ���� EDA оƬ�O(sh��)Ӌ�o����ɡ�EDA �c�a(ch��n)�I(y��)朵ľo�ܽY(ji��)���ѳɞ�����O(sh��)ӋЧ�ʡ��ӿ켼�g(sh��)�M�����P(gu��n)�I�(q��)������

EDA �����·�����·�ĸ������档���O(sh��)Ӌ�����a(ch��n)�^���У�EDA ������оƬϵ�y(t��ng)�������O(sh��)Ӌ�����졢���b�͜yԇ�^�̣�����оƬ�O(sh��)Ӌ��˾�;��A�S���O(sh��)Ӌܛ���������ϵ�y(t��ng)���������EDA ����оƬ����оƬģ�K��ӡˢ�·��PCB�����Ӱ塣

EDA �ܗUЧ���ͽ�(j��ng)��Ч���@��������(j��) ESD Alliance �� WSTS ��(sh��)��(j��)��2020 ��ȫ�� EDA �Ј�Ҏ(gu��)ģ�H�� 115 �|��Ԫ���s�˄��� 4404 �댧�w�ИI(y��)�Ј�Ҏ(gu��)ģ1�|��Ԫ��һ�� EDA �a(ch��n)�I(y��)朻��A(ch��)���F(xi��n)���}�����������·�a(ch��n)�I(y��)���ܵ��ش�Ӱ푣�EDA �ИI(y��)Ҳ�� �����ױ���������ӵ��P(gu��n)�I�I(l��ng)���⣬EDA ��(ji��)�sоƬ�O(sh��)Ӌ�ɱ�������Ҫ���� �����á�����(j��)���ݴ�Wʥ�����У Andrew Kahng ������ 2013 ����Ɯy��2011 ���O(sh��)Ӌ ���M������̎����оƬ�ijɱ��s 4,000 ��������]һ�f��Ԫ 1993 ���� 2009 ��� EDA ���g(sh��)�M�������P(gu��n)�O(sh��)Ӌ�ɱ����ܸ��_ 77 �|��Ԫ��EDA ���g(sh��)�M��������O(sh��)ӋЧ�� 200 ��������˼�Ƽ���Synopsys��2021 �� 8 ���Ƴ��� EDA �O(sh��)Ӌƽ�_ DSO.ai ���磬ͨ�^�����˹����ܣ�оƬ�O(sh��)Ӌ����Ҫ��ȫģ�M�o��(sh��)���ܵIJ��֣�оƬ�O(sh��)Ӌ�������о����M�� �аl(f��)�ɱ��p�룬�аl(f��)�r�g�������ԏ� 24 ���p�ٵ� 2 �ܡ�

1.2. EDA �ķ��

ᘌ���ͬ��͵�оƬ��EDA �в�ͬ�Ĺ��ߡ������·оƬ��Integrated Circuit Chip�� ���Q IC���ĽY(ji��)��(g��u)�Ͽ��Է֞锵(sh��)�� IC��ģ�M IC �͔�(sh��)ģ��� IC����(sh��)�� IC ָ���ڂ�ݔ������ ̎�픵(sh��)����̖(0) �� 1 ���B�m(x��)��̖) IC��ģ�M IC ָ̎����Ȼģ�M��̖�����B�m(x��)�⡢�����ٶȺ͜ض� IC����(sh��)ģ��� IC ָͬ�r����ģ�M�·�͔�(sh��)���·�IJ��� IC����(sh��)ģ��� IC ͨ����ģ�M�·�ǿ���ģ�M�·���F(xi��n)�ض��㷨�ĺ��ġ��� IC �O(sh��)Ӌ���֣�EDA ܛ����Ҫ��ģ�M IC �͔�(sh��)�� IC ����O(sh��)Ӌܛ����

оƬ�O(sh��)Ӌ�֞�ǰ���O(sh��)Ӌ�ͺ���O(sh��)Ӌ������(j��)���w�Ĺ�˾�ͮa(ch��n)Ʒ��ǰ���O(sh��)Ӌ�ͺ���O(sh��)Ӌ�]�нy(t��ng)һ����Ľ��ޡ�һ����f�����O(sh��)Ӌ���·���F(xi��n)���뷨��ǰ���O(sh��)Ӌ�������O(sh��)Ӌ���·�Ǻ���O(sh��)Ӌ���@�����췿�ݣ������O(sh��)Ӌ�D����ǰ���O(sh��)Ӌ���O(sh��)Ӌ���ݵ��ⲿ�Π�̓�(n��i)���Y(ji��)��(g��u)������ʩ���D���ں���O(sh��)Ӌ��Ԕ����B��ʩ�����E�������Ͳ��ϵĔ�(sh��)�����x��

оƬ�O(sh��)Ӌ�ɷ֞��傀�ӴΡ��O(sh��)Ӌ� EDA ����(j��)�O(sh��)Ӌ�����IJ�ͬ�����߿��Ը���(j��)�O(sh��)Ӌ�Ӵ����϶����Mһ�����֞��О鼉��ϵ�y(t��ng)����RTL �ȼ����T�������w�ܼ� EDA ���ߡ����Ӽ� EDA ģ�M����C���ߵľ���������ߣ��ٶ����ν��ͣ��M���F(xi��n)��Ŀ�˺͑��È���Ҳ��ͬ�����磬��ϵ�y(t��ng)���О�ģ�M��C��Ҫ�m���ڮa(ch��n)Ʒ�O(sh��)Ӌ������ԭ����C���u�r�a(ch��n)Ʒԭ�͵����ܺ��ܣ��ײ����w��ģ�M��C��Ҫ�Q����K�a(ch��n)Ʒ�����ܺ������ʡ����ڴ��ͼ����·���O(sh��)Ӌ����ͨ����ϵ�y(t��ng)���О鼉�O(sh��)Ӌ�_ʼ�������O(sh��)Ӌ��ģ�M����C�͌��F(xi��n)����ݔ���ɽ����ľ��w�ܼ�������Ϣ��

��(sh��)��оƬ��ģ�MоƬ���O(sh��)Ӌ�^�̷dz���ͬ�� IC �����O(sh��)Ӌ��Ҫ��ɣ� ���O(sh��)Ӌ���Ľ�(j��ng)�Ҫ�������^�ͣ��o��ע���T/���w�ܼ����ú�·�ɵļ���(ji��)�� IC �O(sh��)Ӌͨ���漰��ÿ���·�Ă��Ի����ԣ�����ÿ�����w�ܵijߴ�ͼ���(ji��)���O(sh��)Ӌ����C������s�����O(sh��)Ӌ���Ľ�(j��ng)�Ҫ����ߡ�

оƬ�O(sh��)Ӌ�ɷ֞�ȫ���ơ��붨���O(sh��)Ӌ��ȫ������Ҫ����ģ�MоƬ���붨�����ڔ�(sh��)��оƬ��ȫ�����O(sh��)Ӌ��ָ�Ծ��w�ܼ�����A(ch��)���ֹ��������������ͻ��B���֡��@�N�O(sh��)Ӌ���S��������ֹ���ɵģ�������ֱ�����ìF(xi��n)���·�ĽY(ji��)�����O(sh��)Ӌ�����L���ɱ��ߡ�ȫ�����O(sh��)Ӌ������ģ�M IC �͔�(sh��)ģ��� IC���붨���O(sh��)Ӌ���T��к͘˜ʆ�Ԫ����A(ch��)������(j��)�Ñ���Ҫ�Ĺ����B�ӳ��샞(y��u)���Ć�Ԫ���붨���O(sh��)Ӌ�ɱ��ͣ����ڶ̣�оƬ�����ʵͣ��m��С�������������a(ch��n)�������ڔ�(sh��)�� IC��

���ڔ�(sh��)��оƬ���ڳ��e����ɵģ����Ҍ��Ԅӻ��̶��и��ߵ�Ҫ�����Ԕ�(sh��)��IC�EDA ���ߵļ��g(sh��)�T��

1.3. EDA �Ěvʷ���� CAD �� EDA

��һ�A�Σ�Ӌ��C�o���O(sh��)Ӌ��CAD���r�����ڼ����·���õ������A�Σ������·���ɶ��^�ͣ��O(sh��)Ӌ�������ȹ������O(sh��)Ӌ���ֹ���ɡ�20 ���o 70 ��20���o�����_ʼ���S��оƬ���ɵ���ߣ��O(sh��)Ӌ���_ʼ�Lԇ�Ԅӻ������O(sh��)Ӌ�Ŀ����ʹ��Ӌ��C�o���O(sh��)Ӌ ��CAD���O(sh��)Ӌ���w�ܼ���D��PCB �������O(sh��)ӋҎ(gu��)�t�z�顢�T���·ģ�M�c�yԇ�����̡�

�ڶ��A�Σ�Ӌ��C�o�����̣�CAED���r����1980 �꿨�������º��ա����S�l(f��)�� ������Ҏ(gu��)ģ�����·ϵ�y(t��ng)��Փ�����ͨ�^�����Z���M��оƬ�O(sh��)Ӌ Ӌ���Ԅӻ��l(f��)չ����Ҫ��־��EDA �ڴ����g������Ҳ�_ʼ�̘I(y��)����ȫ�� EDA ��˼�Ƽ��I(l��ng)���S����˼�Ƽ��I(l��ng)���S�̣�Synopsys����������ӣ�Cadence�������T�� EDA��2017 ����ُ�� MentorGraphics���քe�� 1986 �ꡢ1988 ��� 1981 ��������������

�����A�Σ�����O(sh��)Ӌ�Ԅӻ���EDA���r����20 ���o 90 оƬ���ɶȵIJ�����ߺͿɾ���߉�����ďV������ EDA ���g(sh��)����˸��ߵ�Ҫ��Ҳ���M�˼��g(sh��) EDA �S���O(sh��)Ӌ���ߵ��ռ��Ͱl(f��)չ���Ը��Z��������ϵ�y(t��ng)��ģ�M�;C�ϼ��g(sh��)������ EDA ���g(sh��)��

�����A�Σ��F(xi��n)�� EDA �r����21 ���o�ԁ���EDA ���ߵĿ��ٰl(f��)չ؞���˼����·�O(sh��)Ӌ��������ܷ�yԇ�����Эh(hu��n)��(ji��)�����ڔ�(sh��)�|������(sh��)�ك|���w��Ҏ(gu��)ģ��оƬ�O(sh��)Ӌ��EDA �� �����C�˸��A�κ͌Ӵ��O(sh��)Ӌ�^�̵Ĝʴ_�ԣ��������O(sh��)Ӌ�ɱ����s�����O(sh��)Ӌ���ڣ�������O(sh��)ӋЧ�ʣ��Ǽ����·�ИI(y��)�a(ch��n)�ܺ������M����ԴȪ��EDA ���ߵİl(f��)չ�����˼����·�a(ch��n)�I(y��)�ļ��g(sh��)��(chu��ng)�¡�ͬ�r���S�������֙C��4G/5G����(li��n)�W(w��ng)�ȼ��g(sh��)�İl(f��)չ�����l EDA ܛ��ӭ���˰l(f��)չ���S���A�Ρ�

1.4. EDA ����Y(ji��)�����M���g(sh��)

Ħ���r���ļ��g(sh��)���M�(q��)�� EDA �Uչ���g(sh��)���á���Ħ���r�������·���g(sh��)�İl(f��)չ������Ҫ�������m(x��)Ħ�����ɡ��UչĦ�����ɺͳ�ԽĦ�����ɡ���Ҫ�l(f��)չĿ�˰�������Ħ�����ɵ����a(ch��n)��ˇ�����ߴ���Mһ���s��������ϵ�y(t��ng)���ɵĶ�ܞ�Ŀ�˵�оƬ���ܵĶ��ӻ��l(f��)չ���Լ��O(sh��)�书�ܵļ��ɺͮa(ch��n)Ʒ�Ķ��ӻ������У��挦Ħ�����ɵ����m(x��)����оƬ�ļ���Ҏ(gu��)ģ�ʱ�ը�����L EDA �����ߵ��O(sh��)ӋЧ������˸��ߵ�Ҫ���S��߉��ģ�M���惦�ȹ��ܯB�ӵ�ͬһоƬ�Uչ����EDA ���ߑ����и�����֧�֏��s�����O(sh��)Ӌ���������¹�ˇ���²��ϡ����O(sh��)��ȵđ���Ҫ��ԽĦ�����ɡ� EDA ��ģ�M����C���P(gu��n)�I�h(hu��n)��(ji��)���F(xi��n)������(chu��ng)�¡�

��Ħ���r����ϵ�y(t��ng)�O(sh��)Ӌ EDA ���g(sh��)׃��������ԭĦ�����ɵĶ��x�£�оƬ���ܵ�������Ҫ���Թ�ˇ�ͼܘ�(g��u)������ˇ��ˇ�������ӽ��O�ޣ�Ħ���������@�ž����ڴ˱����£���܇���˹����ܵ��I(l��ng)��Ĵ�˾�_ʼ�����Լ�����ϵ�y(t��ng)��������ҕ�����������P(gu��n)�I���ء���ˣ����� EDA ���������́��f������λ��оƬ�O(sh��)Ӌ�D(zhu��n)׃?y��u)����ܛӲ���f(xi��)����ϵ�y(t��ng)���O(sh��)Ӌ��δ������Ҫ�l(f��)չ����

AI ���M���Ƽ��g(sh��) EDA �������ܻ����Ԅӻ���AI ���ܵ�Ŀ�ˁ��ԬF(xi��n)�� EDA ��ʹ���^���У�оƬ�ܘ�(g��u)̽�����O(sh��)Ӌ�����ֵ��؏��ԡ��̈́�(chu��ng)���Թ���������������ͣ����� AI �ԄӼܘ�(g��u)̽�����O(sh��)Ӌ���ɺ������O(sh��)Ӌ�㷨���S��оƬ�O(sh��)Ӌ���s�Ե���ߣ���(sh��)��(j��)����Ӌ���������������Ƽ��g(sh��)��ʹ��ʹ EDA ԓܛ�����Џ���Ӌ�㡢��ȫ�惦�����ٸ��µȹ��ܣ��ԝM���(sh��)��(j��)����Ӌ�����µĸ���ʹ��Ҫ��

ƽ�_���ͷ���(w��)�����F(xi��n)�� EDA �ǡ����ߺ� IP ���ϰ�������δ���l(f��)չ EDA ƽ�_��EDA �����ήa(ch��n)�I(y��)朵��O(sh��)Ӌ�����졢�yԇ�����b�����ӷ��㣬�YԴ������ͬ�r EDA ԓƽ�_����朽Ӳ�ͬ�O(sh��)Ӌ������ȏS�ҵęM��朽ӣ����M���B(t��i)���O(sh��)���mȻ���ܻ�������ߣ�������Ҫ�˹�֧�ֺͷ���(w��)������(w��)ƽ�_�Ľ��O(sh��)�����ṩ���I(y��)����ԃ�O(sh��)Ӌ����(w��)�����P(gu��n)�Ķ��Ʒ���(w��)���ԝM�む�Ի�������

2.ȫ��EDA���^�Ŕ��Ј�����EDA�Ј��������L

2.1. ȫ�� EDA �Ј���(w��n)���l(f��)չ��������^�Ŕ�

2020 ��ȫ�� EDA �Ј�Ҏ(gu��)ģ�� 115 �|��Ԫ���M�뷀(w��n)���l(f��)չ�ڡ�����(j��) ESDAlliance ��(sh��)��(j��)��2020 ��ȫ�� EDA �Ј�Ҏ(gu��)ģ�� 115 �|��Ԫ��2010-2020 �� 10 ��ͺ����L�ʞ� 8%������(j��) Verified Market Research ��(sh��)��(j��)��2028 ��ȫ�� EDA �AӋ�Ј�Ҏ(gu��)ģ���_�� 215.6 �|��Ԫ��2020-2028 �� 8 ��ͺ����L�ʞ� 8.21%�����ā��f��ȫ�� EDA �Ј����L������(w��n)����

��(sh��)�� IC �� EDA �Ј�����Ҫ�M�ɲ��֡�����(j��)����оƬ�Ј���r����(sh��)��оƬռ��(j��)�˴��Ј����~�� WSTS ��(sh��)��(j��)��2020 �ꔵ(sh��)��оƬ�Ј�Ҏ(gu��)ģ�_�� 3055.68 ���w�����·�Ј�ռ1�|��Ԫ 84.59%����(sh��)������������Ӱ� IC ��(g��u)���� EDA ����(j��)�Ј�����Ҫ���֣� ESD Alliance ��(sh��)��(j��)��2019 ȫ�ꔵ(sh��)������ EDA �_���I(y��)��(w��)Ҏ(gu��)ģ 36.04 1�|��Ԫռ���w�Ј� 52.8%��

ȫ�� EDA ����(j��)�I(y��)��(w��)ˮƽ����I(y��)���¿��Է֞�������ꠡ���һ����ɵ�һ��M�ɡ� Synopsys�� Cadence��Siemens EDA ���҇��H֪�� EDA ��I(y��)�M�ɡ��@���I(y��)�鲼������أ����Ќ����ۺ�ȫ�^�� EDA 2020�꣬�a(ch��n)Ʒ��ijЩ�I(l��ng)��̎���I(l��ng)�ȵ�λ ������Ҏ(gu��)ģ�_�� 10-40 �|��Ԫ���ڶ������ ANSYS��Silvaco��Aldec Inc.�����A������������@���I(y��)���ض��I(l��ng)����ȫ�^�� EDA 2020��a(ch��n)Ʒ�ھֲ��I(l��ng)��̎���I(l��ng)�ȵ�λ ������Ҏ(gu��)ģ�� 0.5-5 �| ��Ԫ�^(q��)�g����������� Altium��Concept Engineering���ł���ӣ��V����˼��о�� DownStream Technologies �����@���I(y��) EDA ����IJ�����Ҫ���c���ߣ�ȱ�� EDA 2020���ض��I(l��ng)��ȫ���̮a(ch��n)Ʒ ��������� 0.5 �|��Ԫ��

������^�Ŕ�ȫ�� EDA �Ј�������(j��) ESD Alliance ��˼�Ƽ��cǰհ�Ԯa(ch��n)�I(y��)�о�����(sh��)��(j��)��Synopsys����������ӣ�Cadence���c���T�� EDA��2016 ����ُ�� Mentor Graphics�� ������^ 2020 ��ȫ�� EDA �Ј��I�շ��~�ı����s�� 70%��������^��������Ψһ���е� Ӌȫ���� EDA ������I(y��)ȱ�������O(sh��)Ӌȫ�^�̹����g(sh��)�Č�����

���У�Synopsys(ֱ�����ڏ��sоƬϵ�y(t��ng)(SoCs)���_�l(f��)��Synopsys ߉�C�Ϲ��� DC(design compiler)���r�������� PT(Prime Time)��ȫ�� EDA �Ј��J �ɶ��^�ߡ�Cadence�a(ch��n)Ʒ���w������O(sh��)Ӌ�������^�̡�ȫ��֪���İ댧�w�����ϵ�y(t��ng)��˾ Cadence ܛ������ȫ���O(sh��)Ӌ�Ę˜ʡ�Mentor Graphics(�������H��2016 �mȻ�����T������ُ�Ĺ��߲���ȫ�棬����ijЩ�I(l��ng)���� PCB(ӡˢ�·��)�O(sh��)Ӌ���ߵȷ�����������עĿ�Ī����ԡ�

ȫ�� EDA ��һ�S�� Synopsys(��˼�Ƽ�)����˼�Ƽ������� 1986 �꣬�� 2008 ��� ȫ������������һ EDA ܛ���S�̡�2020 ����˼�Ƽ������ 36.85 �wĸ�������|��Ԫ 6.63 �|��Ԫ��2020 ����ȫ�� EDA �Ј�������~�� 32%����˼�Ƽ��a(ch��n)Ʒ����ȫ�棬��������Ψһһ�Һ��w�Ĺ����a(ch��n)��оƬ�yԇ���O(sh��)Ӌȫ�^�̵Ĺ�˾ EDA ��˾�Įa(ch��n)Ʒ��(y��u)���w�F(xi��n)�ڔ�(sh��)��ǰ�ˡ���(sh��)�ֺ�ˡ���C�yԇ�ȭh(hu��n)��(ji��)��

����(j��ng)�İ��� Cadence(�������)��Cadence �� 1988 ���� SDA �c ECAD �ɼҹ�˾�ϲ���Cadence ͨ�^һϵ�в�ُ���� 1992 ��ɞ� EDA �ИI(y��)�����һ�İ��������� 2008 �걻 Synopsys ��Խ��2020 ��I�՞� 26.83 �wĸ�������|��Ԫ 5.91 �|��Ԫ��Cadence �����·�͵؈D�O(sh��)Ӌ�ă�(y��u)�c��ģ�M�ͻ����̖��

Mentor Graphics(�������H��2016 �걻�����T����ُ)��Mentor Graphics �� 1981 �������20 ���o 90 �ڽ�(j��ng)�I���y�r�ڣ��a(ch��n)Ʒ�аl(f��)������ИI(y��)�������֣������L�ڿ͑���ʧ���y���c�����ɼҹ�˾������ֱ�� 1994 ��˾�M���Y(ji��)��(g��u)���{(di��o)�������������Mentor Graphics 2016 2016�걻���T����ُ�����P(gu��n)ؔ��(w��)��(sh��)��(j��)���نΪ���¶�� ��I�՞� 12.82 �wĸ�������|��Ԫ 1.55 �|��Ԫ��Mentor Graphics ������C�� PCB �I(l��ng)��(y��u)�����@��

2.2. �Ї� EDA �Ј��������L�����a(ch��n)���ʘO��

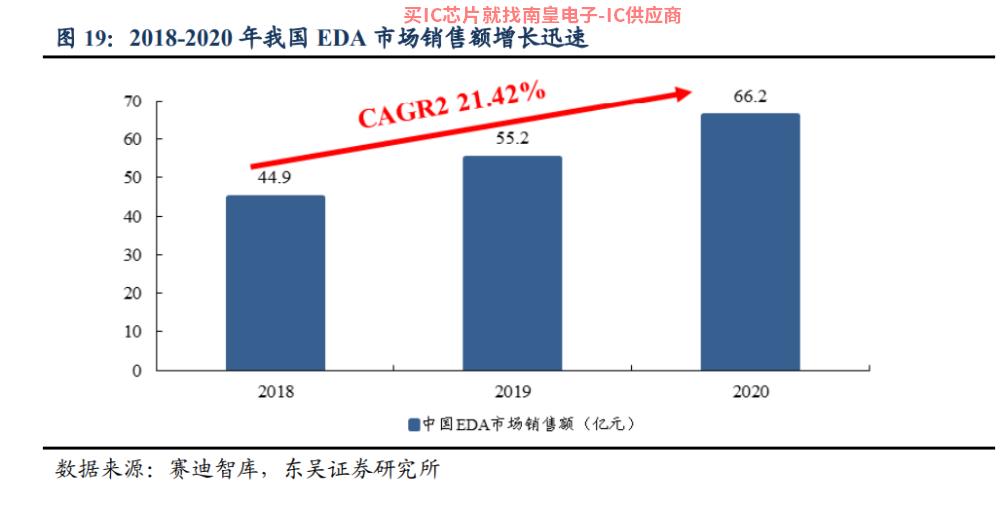

�c���H�Ј���ȣ��Ї� EDA �Ј�Ҏ(gu��)ģ���L���졣����(j��)ِ���ǎ씵(sh��)��(j��)��2018�� �꣬�҇� EDA �Ј����N���~�� 44.9 �|Ԫ������ 2020 ���҇� EDA �Ј��N���ѽ�(j��ng)�_�� 66.2 �| Ԫ��2 ��ͺ����L�ʞ� 21.42%�h����ȫ���Ј�����Ҏ(gu��)ģ 2018-2020 �� 2 �� �ͺ����L��9%��

�Ї� EDA �Ј���λ�ʺܵͣ�������^��Ȼ�Ŕࡣ�mȻ�Ї� EDA �Ј���������L���h����ȫ�����L�ʣ��������Ї� EDA ���������^�����ڮa(ch��n)Ʒ���ܺ����B(t��i)�f(xi��)�{(di��o)����̎���ӄݣ�����(n��i)�Ј����~��Ҫ�ɇ���������ռ��(j��)������(j��)ِ���ǎ��ǰհ�Ԯa(ch��n)�I(y��)�о����Ĕ�(sh��)��(j��)��2020�� ����H EDA ������^ Synopsys��Cadence �� Siemens EDA �҇�������Ҏ(gu��)ģ�� ���ݱ����� 78%�ć��a(ch��n)�S�Ҳ���78% 15%�����a(ch��n)���ʘO�ͣ����a(ch��n)������g�V韡�

2.3. IP �I(y��)��(w��)�� EDA �����L�O

Ӌ��C�o�����̣�CAE���� IP �� EDA �Ј��I(y��)��(w��)����Ҫ�M�ɲ��֡�EDA �Ј��I(y��)��(w��)�ɷ֞�Ӌ��C�o�����̣�CAE����IC �����O(sh��)Ӌ�c��C��PCB �c��оƬģ�K�댧�w IP �˵ȡ�����(j��) ESD Alliance �ļ����I(l��ng)���������(sh��)��(j��)��EDA �������I(l��ng)������ռ�Ȼ������� ���ַ�(w��n)����2020 ��ռ��(j��)�Ј�Ҏ(gu��)ģ�^��IJ����� CAE �c IP�����߿������ӽ� 67%������ CAE��Computer Aided Engineering����Ҫ�������ϵ�y(t��ng)���O(sh��)Ӌ�;C����C���O(sh��)Ӌݔ�롢߉��C��ģ�M�ͻ����̖ģ�M������ʽ��C�����/ģ�M�������yԇ/�yԇ�Ԅӻ��O(sh��)Ӌ��IP��Intellectual Property Core����оƬ�O(sh��)Ӌ�D�Ъ��������·ģ�K�ij����O(sh��)Ӌ���O(sh��)Ӌ�����Գ��� IP �ڶ������sоƬ���·�O(sh��)Ӌ�D���Б���ģ�K�O(sh��)Ӌ���ɱ�����s�؏͵��O(sh��)Ӌ�������s���O(sh��)Ӌ���ڣ����оƬ�O(sh��)Ӌ�ijɹ��ʡ�IP �I(y��)��(w��)�� 2010 ���_ʼ�� EDA �Ј���������_ʼ������ֱ�� 2020 ���ѽ�(j��ng)�_�� 35.22%�ɞ������������ �I(y��)��(w��)�I(l��ng)��

IP �ѳɞ麣�� EDA ��˾����Ҫ���롣Synopsys �� Cadence �� IP ����ռ������ı����������ӣ��e�� Synopsys��2020 �꣬Synopsys �� IP ����ռ������ı������_�� 33%��Synopsys ���� IP �I(y��)��(w��)���ָ��ӷ�(w��n)�� EDA ȫ���Ј��I(l��ng)�ȵ�λ������ ���^�е� Mentor Graphics ���� IP ��ͬ 2004 �x���x���˳� IP �Ј�Ҳ��һ���̶��ό�������K�ĽY(ji��)�� Siemens ��ُ�Y(ji��)����

3.������EDA��ʢ֮·��EDA���I(y��)�l(f��)չҎ(gu��)��

3.1. ����֧���ǻ�ʯ

�������ҿƌW����ÿ���ṩ�����Y��֧�֡��������ҿƌW����NSF����Ҫؓ؟�� ����(j��) IEEE �������ҿƌW����NSF���� 1984 ���� 2015 ���g�� ֧���� 1190 ���c EDA �����P(gu��n)�о��n�}����Ͷ�Y�s�� 800 �f��Ԫ�� 1200 �f��Ԫ��

�댧�w�о�(li��n)�˴��M��I(y��)���м��g(sh��)��(chu��ng)�¡��� NSF ���⣬�댧�w�о�(li��n)�ˣ�SRC��Ҳ������ EDA �������ИI(y��)�İl(f��)չ��SRC �������I(l��ng)�ȵĴ�W�댧�w�����P(gu��n)���g(sh��)�о�(li��n)�ˣ� �Ǵ��M�����댧�w���Լ��g(sh��)�l(f��)չ���P(gu��n)�I���������ИI(y��)�������������ò��Ϲ�˾ AM�����_���� GLOBALFOUNDRIES��IBM��Ӣ�ؠ�������Ƽ��������� �x����˾��(li��n)�ϼ��g(sh��)��˾��SRC �������ИI(y��)�YԴ���۽����Եĸ���ǰ�I(l��ng)��l(f��)�]���P(gu��n)�I���� EDA ��I(y��)ͨ�^ SRC �����о��Y���M�Юa(ch��n)�I(y��)���Լ��g(sh��)��(chu��ng)�¡�

NSF �c SRC ������I(y��)���^�����y�P(gu��n)��NSF �Y���� EDA ���Ŀ���g(sh��)���������ߺ��о��Ŀ��Ҫ̎�ڳ�ʼ�A�Σ�SRC �ɞ�����ߣ��^�m(x��)�o��֧�֡�EDA ��һ�����g(sh��)�ܼ����ИI(y��)��ǰ����Ҫ�������аl(f��)Ͷ�룬�I(y��)��(w��)�؈�С����Ҫ�� NSF��SRC ֧���@�ӵ������C��(g��u)��

���� DARPA ���� ERI Ӌ���� EDA ��I(y��)�^�m(x��)�x�ܡ������������о�Ӌ���֞���ӭ�Ӻ�Ħ�����ɵ�����(zh��n)��DAPRA���� 2017 ��ӏ��dӋ���ꆢ�ӣ�ERI�������S�� 2018- 2023 ���(n��i)Ͷ�Y�s 15 2020�ּ꣬�ڽ�Q�댧�w���g(sh��)�İl(f��)չƿ�i �������h��Ժ���hÿ������һ�� 20 �|��Ԫ���� ERI Ӌ����ERI ԓӋ����Ҫ�����ڲ����c���ɡ��Y(ji��)��(g��u)�c�O(sh��)Ӌ�����P(gu��n)�I���������O(sh��)Ӌ���ֿɷ֞������P(gu��n)�I���� IDEA �c POSH �ɲ��֡�2018 �� 7 �£������� ��ERI������_�����h�x�� ERI ��һ�����֧���Ŀ�����У�Cadence �@���� IDEA �Ŀ 2410 ԓ�Ŀ�����ڄ�(chu��ng)��һ���o���˹����c��оƬ����Ҏ(gu��)����������Synopsys �@���� POSH �Ŀ 610 �a�N1�f��Ԫ��ԓ�Ŀּ�ڌ��F(xi��n)���s���_Դ SoC �ͳɱ��O(sh��)Ӌ��

ע�ش�W�о���������W�о����ľW(w��ng)�j(lu��)�����W�ṩ�����ؔ��֧�֡�2013 �꣬SRC ������ STARnet �������������о�Ӌ����Ӌ����DARPA����W�о����ĵ�Ͷ�Y �W(w��ng)�j(lu��)����Խ 24 ���ݵ� 42 ��W��Ӌ�� 2013-2018 ��Ͷ�Y������W�о����� 1.94 �| �P(gu��n)ע��һ����Ӽ��g(sh��)����Ԫ��STARnet Ӌ���о��ļ��g(sh��)����������δ�� 10-15 ���(n��i)�������̘I(y��)�����ԣ������T���a(ch��n)���� IP ���ڙ�(qu��n)��STARnet Ӌ�� ���c�����о�Ӌ��(FCRP)�������m(x��)��2008 �꣬ȫ������ 5 �� FCRP ���ģ����� GSRC �� C2S2 �����c EDA �@�ɂ����ĵ��Ŀֱ�����P(gu��n) EDA ��Ӌ���P(gu��n)�Y���� 400 �f��Ԫ�� 500 �f��Ԫ֮�g��ͬ�r�� 2018 �� DARPA �l(f��)���� ERI �ڵ�һ���Y�������У�IDEA�c POSH Ӌ���������W�ṩ��ͬ�s�� 6000 �f��Ԫ��

3.2. �˲š����g(sh��)�����B(t��i)�� EDA �ИI(y��)���ĸ���Ҫ��

�˲��� EDA �l(f��)չ�ĺ��ġ�EDA ԓܛ���漰�댧�w����(sh��)�W��оƬ�O(sh��)Ӌ���N֪�R����Ҫ�����@���N֪�R����(j��)�Ї���˼�Ƽ�������(j��ng)���־��������B�����B(y��ng)һ�� EDA �˲Ų����ף��Ĵ�W�n�}�о��������Č��`������Ҫʮ��ĕr�g������(j��)�� 23 ȫ���·���������¶��(sh��)��(j��) EDA ֻ���ИI(y��)�ĘI(y��)�ˆT 4 һ�f�����ң����� EDA �˲����B(y��ng)�wϵ�dz���Ҫ��

����˼�Ƽ���������˼�Ƽ�ע���˲����B(y��ng)�����˲����B(y��ng)��(zh��n)������˼�Ƽ���W�n���wϵ����˼�Ƽ���WӋ���ͷe�O���c�����˲ő�(zh��n)�ԡ���˼�Ƽ��_�l(f��)��һ��ȫ�����·�O(sh��)Ӌ�̳̣����� 131 ���Ƽ��о����n��24�T 37�T��Ӗ�n�� ���Ƽ��Tʿ�о����m���ڼ����·���P(gu��n)���I(y��)����EDA���˲����B(y��ng)�ɹ����ԣ��H2019��- 2020 ���@һ�꣬���� 30000 20�˅��c����˼�Ƽ��˲��Ŀ ����(n��i)��У�c��˼�Ƽ��������˲����B(y��ng)������

���m(x��)�аl(f��)�� EDA �l(f��)չ�Ą�����EDA ܛ�����㷨�ܼ��ʹ����I(y��)ܛ��ϵ�y(t��ng)��EDA Ӌ��C����������(sh��)�W��֪�R��Ҫ�_�l(f��)��оƬ�O(sh��)Ӌ��׃��Խ��Խ�죬EDA ܛ����˾��Ҫ���������аl(f��)Ͷ�Y���Դ_���似�g(sh��)�g(sh��)�I(l��ng)�ȡ�ͬ�r��EDA ���������^�Ĕ�(sh��)�� ֪�R�a(ch��n)��(qu��n)�����I(l��ng)�ȵ�λ��ȫ��������^�Ŕ�ĸ�� 2000 2010-2020���������(w��n)�� ������^��������ͺ����L�ʽӽ� ���Ա���10% �аl(f��)�M����30%-40%�����e��� �ݳ��^ 40%��2020 �꣬Synopsys �� Cadence �аl(f��)�M�÷քe���_ 13 �|�� 10 �|��Ԫ�� ���� 2020 ���Ї� EDA �Ј��N��Ҏ(gu��)ģ�ăɱ���

�a(ch��n)�I(y��)朅f(xi��)ͬ�� EDA ���C�l(f��)չ��оƬ�O(sh��)Ӌ�����M��ˇ�Ǿ��A�S���O(sh��)Ӌ��˾�� EDA ܛ�������̹�ͬ�ƏV�ijɹ������A�S�IJ��ϡ����W����ˇ�����첽�E����ˇͻ�ƣ�EDA ��˾���þ��A�S�Ĝyԇ��(sh��)��(j��)��ˇ����(ji��)�ļ��M�и��M EDA ܛ����оƬ�O(sh��)Ӌ��˾ʹ���µ� EDA �O(sh��)Ӌ��ԇ���a(ch��n)ģ�ͣ������o���A�S�� EDA ���M���칤ˇ��ܛ��ģ�͡����A�S��EDA ܛ����˾���O(sh��)Ӌ��˾���o��ɣ����������ͬ�ƄӼ��g(sh��)�M����

���У�PDK��Process Design Kit���ǜ�ͨ IC �O(sh��)Ӌ��˾��OEM�� EDA �����̵Ę��������w���f��PDK оƬ�O(sh��)Ӌ��һ�M�����댧�w��ˇ����(ji��)���ļ� EDA ����ʹ�á��͑� ���A�S����Ͷ�a(ch��n)ǰʹ�� PDK���_�����A�S�܉����(j��)�͑��O(sh��)Ӌ���a(ch��n)оƬ���_��оƬ �A�ڹ��ܺ����ܡ�PDK �������˷�ӳ����ˇ����Ҫ�أ����w�ܡ����|�ס����B���ȣ� �����O(sh��)ӋҎ(gu��)�t�ļ���늌WҎ(gu��)�t�ļ�����D�Ӵζ��x�ļ�SPICE ģ�Mģ�͡��O(sh��)�䲼�ֺ� ���g���ƅ���(sh��)�������Įa(ch��n)�I(y��)�ʹ�͑� PDK ���Խo�� EDA �S�ҳ�ַ������S�Ҹ���(j��) PDK ���˝M��͑��������M�a(ch��n)Ʒ���@�ø�ȫ���� PDK Ҳ�����^ EDA �S�� ���^��(y��u)�ݡ�

3.3. ��ُ�� EDA �����̔U������Ҫ�ֶ�

��ُ�� EDA ��I(y��)���L������x������������^�ij��Lʷ�Dz�ُʷ������ ȫ�� EDA ���^ Synopsys �� 1986 ������� 2021 �� 4 �£������ 112 ��ُ �� EDA �ИI(y��)��˷��s��ԭ���У�

1)�ИI(y��)С�����I(l��ng)��ܶࡣ����(j��) ESD Alliance �� WSTS ��(sh��)��(j��)��2020 ��ȫ�� EDA ֻ���ИI(y��)�Ј�Ҏ(gu��)ģ 115 �c���ΰ댧�w�ИI(y��)��ȣ�1�|��Ԫ 4404 �| ��Ԫ���Ј�Ҏ(gu��)ģ��һ��С�ИI(y��) EDA ��оƬ�O(sh��)Ӌ���a(ch��n)�������a(ch��n)�I(y��)朷���(w��)ܛ����EDA ���g(sh��)�����L����Ҫ���N�c���������γɹ���朣�ͬ�r���͑�ϣ�� EDA �����̿����ṩ���w��Q������2)���g(sh��)���µ����ٶȿ졣2)���g(sh��)���µ����ٶȿ졣��Ħ�����ɵ��(q��)���£�оƬ�����ٶȿ죬�¼��g(sh��)����ӿ�F(xi��n)�����������O(sh��)Ӌܛ�� EDA ������ÿ�궼ҪͶ��������аl(f��)�Y�����m�����g(sh��)��(chu��ng)�£����S�����(chu��ng)��˾��Ȼ����(chu��ng)���µ��c���ߡ��ИI(y��)��(n��i)�кܶ�С�����I(l��ng)�͑�ϣ�� EDA �������ṩ�����Ľ�Q��������� EDA �S�Ҳ������k�������Լ��Įa(ch��n)�I(y��)朡�Ȼ�����S�����g(sh��)�Ŀ��ٵ������ИI(y��)��(n��i)��С��˾�������턓(chu��ng)���c���ߡ��ИI(y��)С���������аl(f��)���g(sh��)�ɱ��ߣ���ُ������x��

Cadence ͨ�^��ُ�ɞ�һ��������Cadence �� 1989 ����ُ Verilog ͨ�^�@�β�ُ������Ҫ�IJ�ُ Cadence оƬ������C���}�ijɹ���QҲ��־�����s�� EDA ���O(sh��)Ӌ�I(l��ng)�Uչ��ܛ��ģ�M��Ӳ��ģ�M�I(l��ng)���O(sh��)Ӌ��ģ�M����ͨ�^ʹ��ͬһ��˾�IJ�ͬܛ������ɡ�2001 �� Cadence ��ُ Silicon Perspective���� IC ���ֹ��ߺ� SI ���������������У����g(sh��)������һ�����ֲ�����2002 ����ُ Simplex���a���������(sh��)��ȡ�ͷ���������ͬ����ُ IBM ����ռ�I(l��ng)Ӳ������ߵص�Ӳ������I(y��)��(w��)��

Synopsys ��Խ��ُ Cadence���T��ȫ�� EDA ���^��λ���v�^ Synopsys �l(f��)չ�vʷ���Hͨ�^������ُ�����˹�˾�I(y��)��(w��)�����F(xi��n)��ȫ�^�̸��w������ͨ�^�״��P(gu��n)�I��ֱُ�����cʣ���ɴ���^�ĸ�����Ó�f�������ɞ�ȫ�� EDA ���^������(j��)����˼�딵(sh��)��(j��)��2002 �꣬Synopsys �� 8.3 ��ُ1�|��Ԫ Cadence �����V�A�Y(ji��)�� Avanti���Ķ��ɞ� EDA �vʷ�ϵ�һ�������ṩ������피�ǰ��� IC �I(l��ng)�ȵ��O(sh��)Ӌ���� EDA �����̡���ُ��׃�˂��y(t��ng)��Synopsys ռǰ�ˣ�Cadence ռ��˸�֣� Synopsys ���M�뵽 ��ʯ���g(sh��)�IJ����ں�Ħ�����ɕr��֮ǰ������ˡ�

4.���a(ch��n)EDA�ǻ����ԭ

4.1. �����⌦�ȿ����a(ch��n) EDA �F(xi��n)��

���� EDA �������Įa(ch��n)Ʒ��ꇡ��� EDA ����(j��)�҂���Ӌ�㣬�a(ch��n)Ʒ��ꇵ������ԣ�EDA �� ��朴�s�� 40 �ڼ����I(l��ng)����(n��i)�S��߀�]������H����S���ǘӌ��F(xi��n) EDA ���wȫ�^�̡�ȫ�����I(l��ng)���� 2021 �� 12 �£����a(ch��n) EDA ���^�A�����ֻ�܌��F(xi��n)ģ�MоƬ�O(sh��)Ӌ��ƽ���O(sh��)Ӌ��ȫ�^�̸��w�����w�ʼs�� �������a(ch��n)40% EDA �����̵Įa(ch��n)Ʒ������c���ߣ����ܞ�͑��ṩ�ض��I(l��ng)���ȫ�^�̮a(ch��n)Ʒ����(w��)��

���� EDA �a(ch��n)Ʒ֧�ּ��g(sh��)�����M���� EDA �Įa(ch��n)Ʒ���g(sh��)���M�ԁ��������H������^���a(ch��n) �����M��Ʒ��֧�ֹ�ˇ�ѽ�(j��ng)���F(xi��n) 2nm������(n��i)�S��ֻ��һЩ�a(ch��n)Ʒ֧�����M�Ĺ�ˇ�����磬���A�����ģ�M�O(sh��)Ӌ��ȫ�^�̹����У�ֻ��һ���·ģ�M����֧�� 5nm ��ˇ������ֻ֧�� 28nm ��ˇ��˼��о EDA �a(ch��n)Ʒ�H֧�� 10nm �Ƴ̡�

IP �ѳɞ麣�� EDA ��˾����Ҫ�����LJ���(n��i)�� EDA ��˾��δ��Ҏ(gu��)ģ���֡�EDA �����^�е� Synopsys �� Cadence ͬ��Ҳ�� IP �Ј����^��Synopsys �� Cadence IP �Ј� �H��������ڶ��͵���������Ҏ(gu��)ģ���~ ARM�����֮�£����a(ch��n) EDA �����(sh��)�����������_�l(f��)�� EDA ���ߣ��]�в��� IP �a(ch��n)Ʒ���S�������·�a(ch��n)�I(y��)�IJ���l(f��)չ��IP ���Õ�Խ��Խ�@��������(n��i)�� EDA ��˾�� IP �l(f��)չ����^��

���� EDA �a(ch��n)Ʒ�Ȱl(f��)��(y��u)�����@���͑�ճ�Ըߡ��� 20 ���o 70 ܛ�������o���r�� ��оƬ�O(sh��)Ӌ�_ʼ������ EDA �a(ch��n)�I(y��)�l(f��)չ�� 50 �꣬���g(sh��)�����B(t��i)�Ϳ͑��������@���Ȱl(f��)��(y��u)�� ʹ�����T���^���ơ����⣬2021 �����M��ˇоƬ��Ƭ�ɱ����_��(sh��)�|Ԫ�� EDA �����x���c��Ƭ�ijɹ������P(gu��n)���͑����Q EDA ���͑�ʹ�Ç��ҕr�����ߎ������L�U�dz��� �a(ch��n) EDA �ܳ���(sh��)��(j��)�͇��H���^ EDA �����߲�һ�r������(n��i)������������Ҫ��ጽY(ji��)����

����(n��i) EDA ���I(y��)�˲ŅT�����������Y���� EDA ��I(y��)������(j��)ِ���ǎ씵(sh��)��(j��)�� 2020 ���҇� EDA �ИI(y��)�ĘI(y��)�ˆT��(sh��)���s�� 4400 �ˣ����� EDA ��I(y��)��?c��)˔?sh��)�s��2000 �ˡ��mȻ��� 2018 ��� 700 �����˺ܴ�����L�����c�������߀�Ǵ��ڵ� ����^����(j��)�� 23 ȫ���·���������¶��(sh��)��(j��) EDA �ИI(y��)�ĘI(y��) �˔�(sh��)�� 4 һ�f�����ң���ֹ���� 2021 �� 12 �£��H Synopsys �T����(sh��)���_�� 1.5 �f �����ϡ�

�҇� EDA �����˲����B(y��ng)�wϵ�����ơ����� EDA 2015����Ӗ�wϵ�������� �꣬ ���� SRC ������ STARnet Ӌ���������(n��i)Ͷ�Y������W�о����� 1.94 �|��Ԫ�� �����Ŀֱ���c EDA ���P(gu��n)��Synopsys ���M���Ї��ԁ������c���A��W���|�ϴ�W�� �A�пƼ���W��֪����W�����������ṩܛ��֧�֣����������������ġ�Ŀǰ�҇�ֻ�� �ٔ�(sh��)��У�� EDA ����(n��i)�о�������˲����B(y��ng)Ӌ�� EDA ��˾�c��У�ĺ���Ҳ�����_ʼ һ�_ʼ���˲����B(y��ng)�wϵ߀�����ơ�

����댧�w�a(ch��n)�I(y��)朵ąf(xi��)�{(di��o)���Ӿo�ܡ�EDA ܛ�����Ǫ����_�l(f��)�ģ�EDA �cоƬ�O(sh��)Ӌ�S�Һ;��A�S�Һ�������ĥ�a(ch��n)Ʒ�����M���g(sh��)�M��������댧�w�a(ch��n)�I(y��)��Rȫ������Ӣ���_��Ӣ�ؠ��� AMD ߀�����ǡ��_�e늡����_���µȴ��;��A�����̡�������鱾�����Ǽ���܉�������^��I(y��)���ڮa(ch��n)�I(y��)��������P(gu��n)�I���ã��ڏ���ąf(xi��)�{(di��o)�¿������� EDA �a(ch��n)Ʒ�ĸ�������

���� EDA ��ُ�������֡�EDA ������^��Ҫͨ�^��ُ�������Լ��Įa(ch��n)�I(y��)朡���ُ���H��Ҫ�Y��߀��Ҫ���|(zh��)����Ŀ��Ⱥ�w�M�в�ُ������(j��) crunch base ��(sh��)��(j��)��2020 �꣬����� 600 ��ң����� 200 �ܶ�)���@����^��ُ�ṩ���S�������������֮�£��Ї�ֻ�Ў�ʮ�� EDA ����(n��i)��I(y��)��һ���̶���Ҳ�Ƽs�ˇ���(n��i)��I(y��) EDA �a(ch��n)�I(y��)�l(f��)չ��

4.2. EDA ���a(ch��n)�����ڱ���

�����Ƽ�Ó�^��څ���������ҡ��������H�@�^�����Q(m��o)�M����ֱ�ӌ�����������Ї������~����Q(m��o)���P(gu��n)����߀ᘌ��Ї����� �A�顢���dͨӍ�Ȳ�ȡһϵ�����ƴ�ʩ�������Ʋ����Ρ�2019 �� 5 �� 16 �ձ��������̄�(w��)���������A��� 70 ���^�Č��w��ΰ�����ͥ�P(gu��n)(li��n)��I(y��)���]���������������ʣ��A�錢�o����������˾ُ�I�������ܴ�Ӱ푣��S������������_ʼ��A�顣�������Ї��ĉ����ѽ�(j��ng)�Ľ�(j��ng)�Q(m��o)�I(l��ng)���������Ƽ��I(l��ng)�߿Ƽ��ɞ��p�������Ľ��c��EDA ����댧�w�� ���ϵ������Ȼ�ܵ����������ơ�Ŀǰ���A����ֹͣ�c������H���^�ĺ����������о� �l(f��) EDA ���ڱ��С�

�A���Ķ����Ӈ��a(ch��n) EDA ��Ҋ��I(y��)����Ҫ�ԡ� 2020 �� 12 ��1�·��ԁ����A��Ĺ����ѽ�(j��ng)Ͷ�Y���ļ҇���(n��i)��˾ EDA ����ȫ���l�ڃ�(n��i)�Ĺ�˾Murata�������̹����ṩ�̾�ͬ����ӡ���ע�ڹ��I(y��)�O(sh��)Ӌ��ģ�M�ğo�a�w�V��ӡ���ע��߉�C�Ϻ������O(sh��)Ӌ����оܛ���Լ���ע�ڔ�(sh��)��ǰ����C�İ���˹�������LJ���(n��i)�I(l��ng)�ȵļ��ֹ����I(l��ng)�� EDA �S�̡�

4.3. ��ʮ��l(f��)չ��EDA �c�����a(ch��n)֮��

���a(ch��n) EDA ��(j��ng)�^30������D��l(f��)չ��ӭ�������ߺ��Y��֧�֡�EDA �ć��a(ch��n)��·�_ʼ 20 ���o 80 �����20 ���o 90 ��������Ї��vʷ�ϵ�һ����������֪�R�a(ch��n)��(qu��n)���� EDA ������؈�Q�������@�ö�헇��H��헡����S����� EDA ���첻���I��˼���£����a(ch��n)�S���M���Ї� EDA �@���ИI(y��)�ѽ�(j��ng)��Ĭ��ʮ���ꡣֱ�� 2008 ��ȇ��Һ˸��Ŀ EDA ���У����a(ch��n) EDA �a(ch��n)�I(y��)�������l(f��)�������c��ͬ�r��ZTE���A���¼�ʹ�˂����R���P(gu��n)�I���A(ch��) �Y���Ј�Ҳ�_ʼ�P(gu��n)ע���A(ch��)���g(sh��)����Ҫ�� EDA �ИI(y��)������(j��)����˼���о����Ĕ�(sh��)��(j��)��2020�� �� EDA �ИI(y��)���Y�Δ�(sh��)���_�� 16 �Σ��h�� 2010 ��� 1 �Ρ�

���a(ch��n) EDA �ИI(y��)��u�Ѵ��ǻ�����ԭ���ڇ������ߺ��Y�����p��֧���£� �a(ch��n) EDA �S�Ҕ�(sh��)���������ӡ�����(j��)����˼���о����Ĕ�(sh��)��(j��)��2020�� ����(n��i)���мs 49 �� EDA ���� 2021 �� 12 �� 30 �գ�����(n��i)���� 4 ����I(y��)��Ո IPO�����У��ł���������С��@Щ���a(ch��n) EDA �S�� �ĸ��������I(l��ng)��ȡ�ü��g(sh��)ͻ�ƣ������A���������ṩģ�MоƬ�O(sh��)Ӌ��ȫ�^�� EDA �a(ch��n)Ʒ������(j��)ِ���ǎ씵(sh��)��(j��)��2018-2020�� ���Ї� EDA �Ј��I�յć��a(ch��n)�����~��u�� 6%���� �� 11%�����a(ch��n)��������u�ӿ죬�ǻ���ԭ��

- �I(l��ng)�ȵ�SDL�Ԅ��{�

- �A��܇���ˣ����d�A�飿HiCarϵ�y(t��ng)��֧��5G�W(w��ng)�j(lu��)��

- Ӣ�ؠ�CEO���¾��A�S�O(sh��)��Ľ����r�g������L

- ���_˹�о��ˆT�_�l(f��)������|(zh��)�ӌ��w����Ե��¼��g(sh��)

- ��(sh��)�\�����Ќ��cȼ�ǻ۳��е���(zh��n)��

- ������܇늳�������ACC�x����R���佨��늳�ģ�K���a(ch��n)��

- �cȼAI��(chu��ng)�룬�B�Ӯa(ch��n)�W�Y(ji��)��

- �x�ó��Ї��^(q��)MCUR&D�F�:���ÆT���^�m(x��)Ͷ�Y�Ї��Ј�

- ������ͨ���L�����^Velodyne���ܻ��A(ch��)�O(sh��)ʩ��Q����(IIS)������r

- �O����܇�����Ŀ����څ�ݣ��m������߹���ƸՈǰ����

- �_�P(gu��n)�Դ��ُ���ɼ�ʹ��ע�����

- Nordic���C��(li��n)�W(w��ng)�͵����{���ṩ늚��h����Դ����